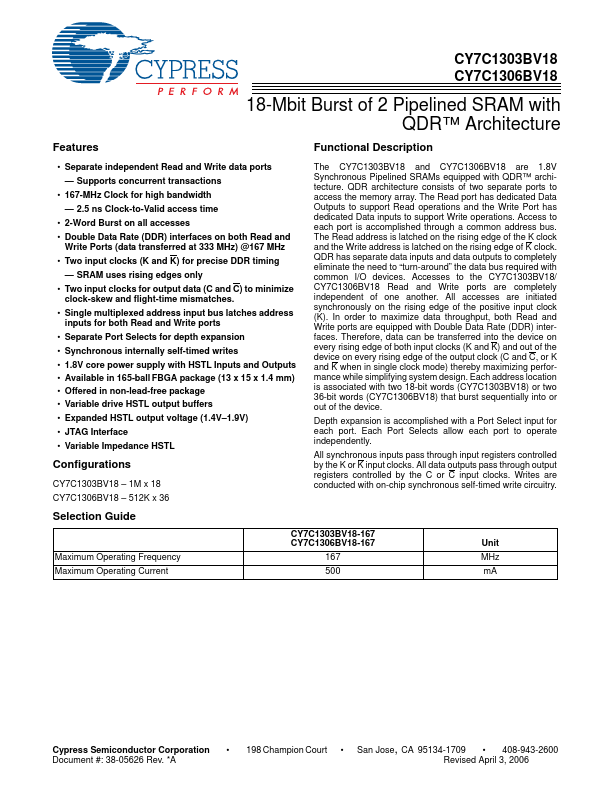

CY7C1306BV18

Overview

- Separate independent Read and Write data ports - Supports concurrent transactions

- 167-MHz Clock for high bandwidth - 2.5 ns Clock-to-Valid access time

- 2-Word Burst on all accesses

- Double Data Rate (DDR) interfaces on both Read and Write Ports (data transferred at 333 MHz) @167 MHz

- Two input clocks (K and K) for precise DDR timing - SRAM uses rising edges only

- Two input clocks for output data (C and C) to minimize clock-skew and flight-time mismatches.

- Single multiplexed address input bus latches address inputs for both Read and Write ports

- Separate Port Selects for depth expansion

- Synchronous internally self-timed writes

- 1.8V core power supply with HSTL Inputs and Outputs