Datasheet Summary

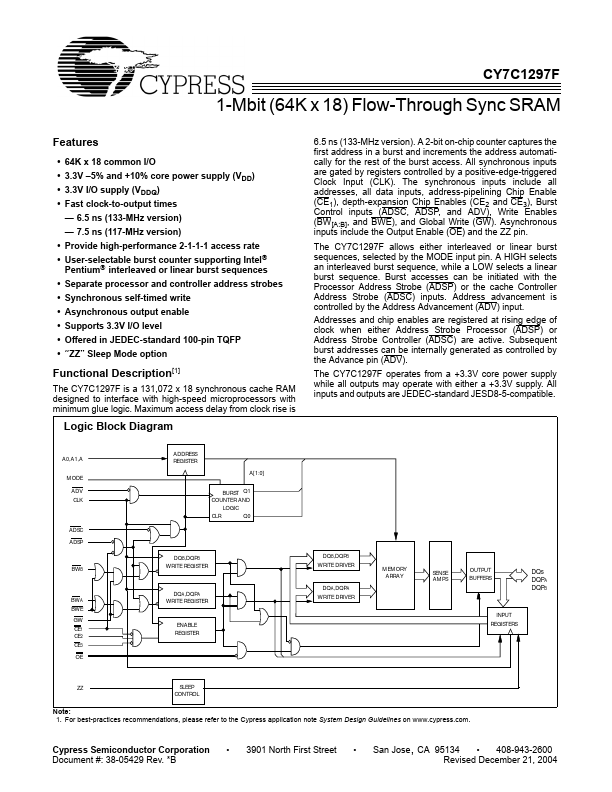

1-Mbit (64K x 18) Flow-Through Sync SRAM

Features

- 64K x 18 mon I/O

- 3.3V

- 5% and +10% core power supply (VDD)

- 3.3V I/O supply (VDDQ)

- Fast clock-to-output times

- 6.5 ns (133-MHz version)

- 7.5 ns (117-MHz version)

- Provide high-performance 2-1-1-1 access rate

- User-selectable burst counter supporting Intel Pentium interleaved or linear burst sequences

- Separate processor and controller address strobes

- Synchronous self-timed write

- Asynchronous output enable

- Supports 3.3V I/O level

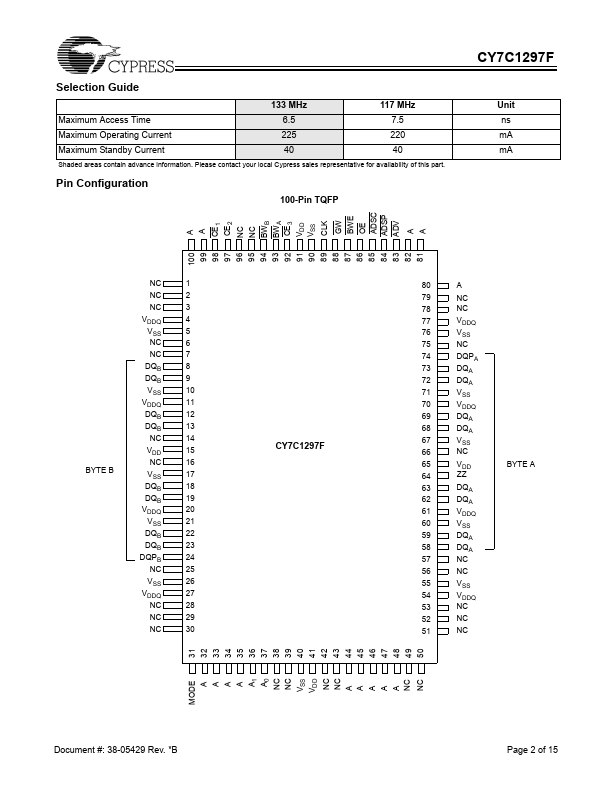

- Offered in JEDEC-standard 100-pin TQFP

- “ZZ” Sleep Mode option 6.5 ns (133-MHz version). A 2-bit on-chip counter captures the first address in a burst and increments the address...