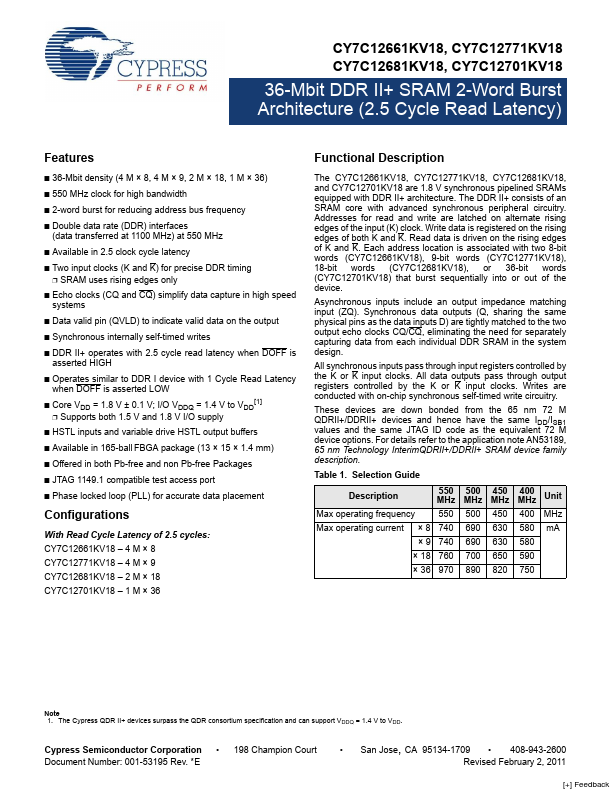

CY7C12701KV18 Overview

Key Specifications

Package: FBGA

Mount Type: Surface Mount

Pins: 165

Operating Voltage: 1.8 V

Key Features

- 36-Mbit density (4 M × 8, 4 M × 9, 2 M × 18, 1 M ×

- 550 MHz clock for high bandwidth

- 2-word burst for reducing address bus frequency

- Double data rate (DDR) interfaces (data transferred at 1100 MHz) at 550 MHz

- Available in 2.5 clock cycle latency