CY7C1010DV33

Overview

- Pin and function compatible with CY7C1010CV33

- High speed ❐ tAA = 10 ns

- Low active power ❐ ICC = 90 mA at 10 ns

- Low CMOS standby power ❐ ISB2 = 10 mA

- 2.0 V data retention

- Automatic power down when deselected

- TTL-compatible inputs and outputs

- Easy memory expansion with CE and OE features

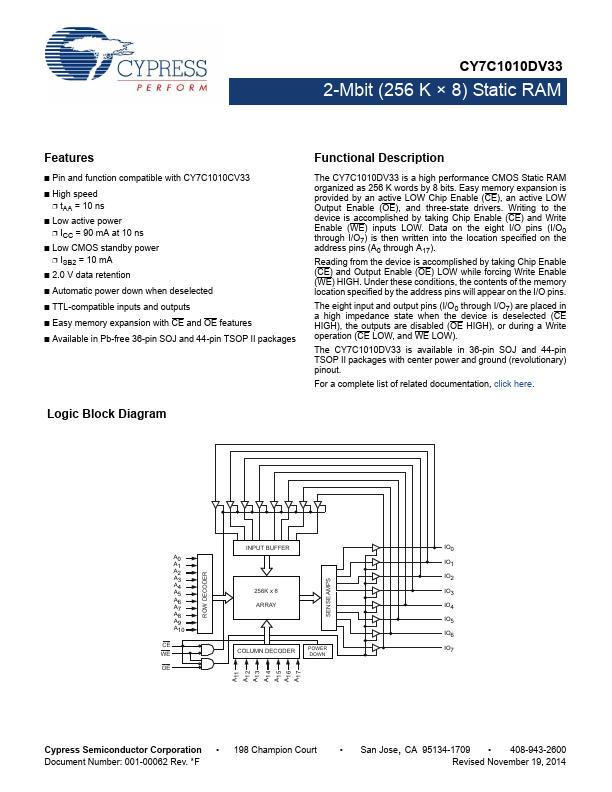

- Available in Pb-free 36-pin SOJ and 44-pin TSOP II packages Functional Description The CY7C1010DV33 is a high performance CMOS Static RAM organized as 256 K words by 8 bits. Easy memory expansion is provided by an active LOW Chip Enable (CE), an active LOW Output Enable (OE), and three-state drivers. Writing to the device is accomplished by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. Data on the eight I/O pins (I/O0 through I/O7) is then written into the location specified on the address pins (A0 through A17). Reading from the device is accomplished by taking Chip