CS5542

CS5542 is Multi-Channel DS ADC manufactured by Cirrus Logic.

Features

Description

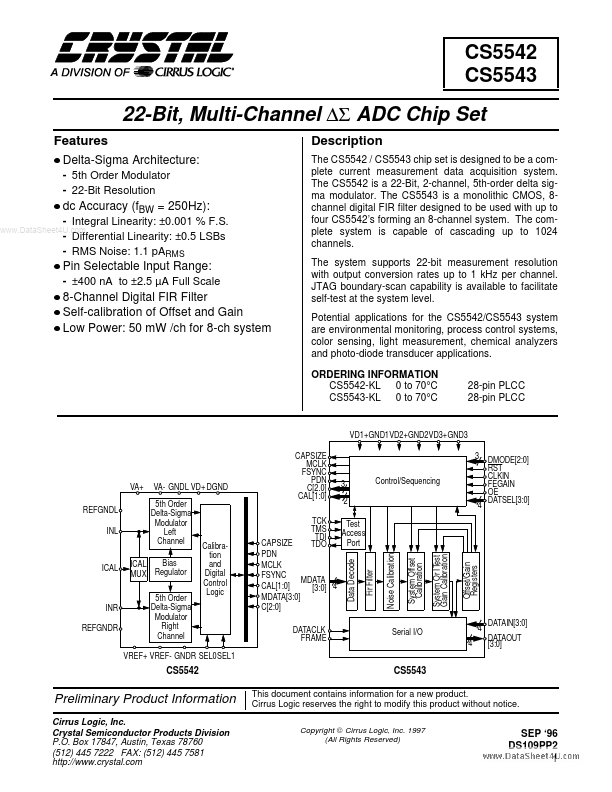

The CS5542 / CS5543 chip set is designed to be a plete current measurement data acquisition system. The CS5542 is a 22-Bit, 2-channel, 5th-order delta sigma modulator. The CS5543 is a monolithic CMOS, 8channel digital FIR filter designed to be used with up to four CS5542’s forming an 8-channel system. The plete system is capable of cascading up to 1024 channels. The system supports 22-bit measurement resolution with output conversion rates up to 1 k Hz per channel. JTAG boundary-scan capability is available to facilitate self-test at the system level. Potential applications for the CS5542/CS5543 system are environmental monitoring, process control systems, color sensing, light measurement, chemical analyzers and photo-diode transducer applications. ORDERING INFORMATION CS5542-KL 0 to 70°C CS5543-KL 0 to 70°C 28-pin PLCC 28-pin PLCC l Delta-Sigma Architecture: l dc Accuracy (f BW = 250Hz):

..

- 5th Order Modulator

- 22-Bit Resolution l Pin Selectable Input Range:

- Integral Linearity: ±0.001 % F.S.

- Differential Linearity: ±0.5 LSBs

- RMS Noise: 1.1 p ARMS

- ±400 n A to ±2.5 µA Full Scale l 8-Channel Digital FIR Filter l Self-calibration of Offset and Gain l Low Power: 50 m W /ch for 8-ch system

VD1+GND1VD2+GND2VD3+GND3 CAPSIZE MCLK FSYNC PDN C[2.0] CAL[1:0] TCK TMS TDI TDO 3 DMODE[2:0] RST CLKIN FEGAIN OE DATSEL[3:0] 4

VA+ REFGNDL INL

VA- GNDL VD+ DGND 5th Order Delta-Sigma Modulator Left Channel

3 2 Test Access Port

Control/Sequencing

Noise Calibration

INR REFGNDR

5th Order Delta-Sigma Modulator Right Channel

Fir Filter

ICAL

Offset/Gain Registers 4 4 DATAIN[3:0] DATAOUT [3:0]

Bias ICAL MUX Regulator

DATACLK FRAME

Serial I/O

VREF+ VREF- GNDR SEL0SEL1

CS5543

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

Copyright © Cirrus Logic, Inc. 1997 (All Rights Reserved)

Preliminary Product Information

Cirrus Logic, Inc. Crystal Semiconductor Products...