CS2501 Overview

Key Specifications

Description

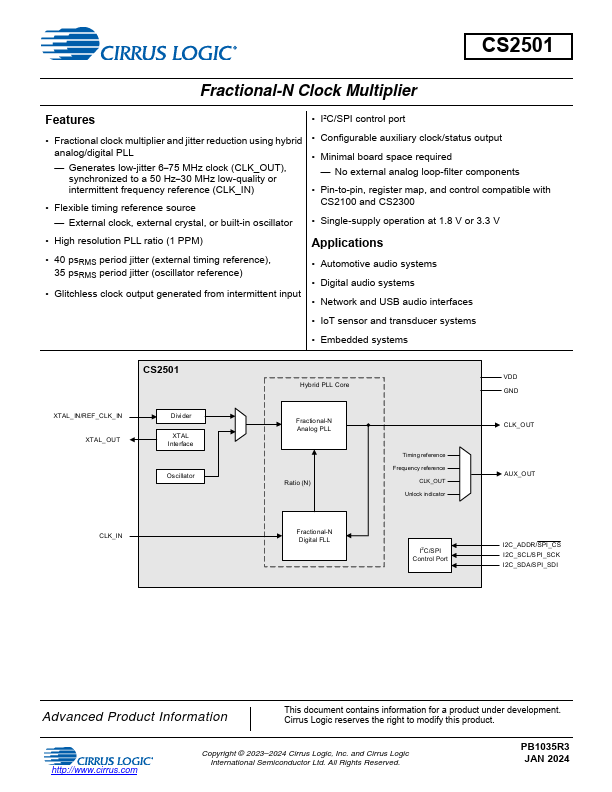

The CS2501 is a system-clocking device incorporating a programmable phase-locked loop (PLL). The hybrid analog/ digital PLL architecture comprises a delta-sigma fractional-N analog PLL and a digital frequency-locked loop (FLL).

Key Features

- I²C/SPI control port

- Fractional clock multiplier and jitter reduction using hybrid analog/digital PLL

- Generates low-jitter 6–75 MHz clock (CLK_OUT), synchronized to a 50 Hz–30 MHz low-quality or intermittent frequency reference (CLK_IN)

- Flexible timing reference source

- External clock, external crystal, or built-in oscillator