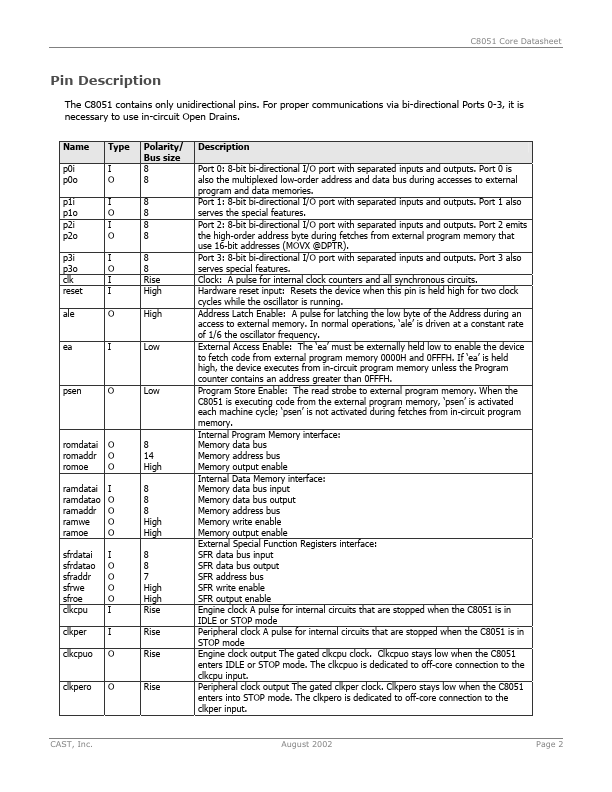

C8051 Description

The C8051 processor core is a single-chip, 8-bit microcontroller that executes all ASM51 instructions and has the same instruction set and timing of the 80C31. On-chip debugging is an option. The microcode-free design was developed for reuse in ASICs and FPGAs.

C8051 Key Features

- 8-bit Control Unit

- 8-bit Arithmetic-Logic Unit with 8-bit

- Instruction decoder

- Four 8-bit Input / Output ports

- Two 16-bit Timer/Counters

- Serial Peripheral Interface in full duplex mode

- Synchronous mode, fixed baud rate

- 8-bit & 9-bit UART mode, variable baud rate

- 9-bit UART mode, fixed baud rate

- Multiprocessor munication