ADS5270 Overview

Key Specifications

Package: QFP

Pins: 80

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

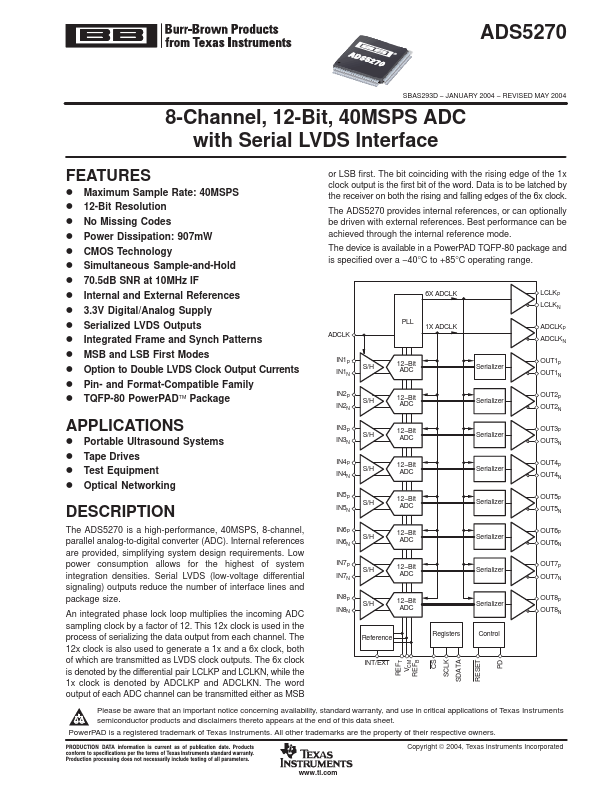

The ADS5270 is a high-performance, 40MSPS, 8-channel, parallel analog-to-digital converter (ADC). Internal references are provided, simplifying system design requirements.

Key Features

- The bit coinciding with the rising edge of the 1x clock output is the first bit of the word

- Data is to be latched by the receiver on both the rising and falling edges of the 6x clock

- The ADS5270 provides internal references, or can optionally be driven with external references

- Best performance can be achieved through the internal reference mode

- The device is available in a PowerPAD TQFP-80 package and is specified over a -40°C to +85°C operating range