AZ100E142

AZ100E142 is ECL/PECL 9-bit Shift Register manufactured by Arizona Microtek.

..

ARIZONA MICROTEK, INC.

AZ10E142 AZ100E142

ECL/PECL 9-bit Shift Register Features

- -

- -

- -

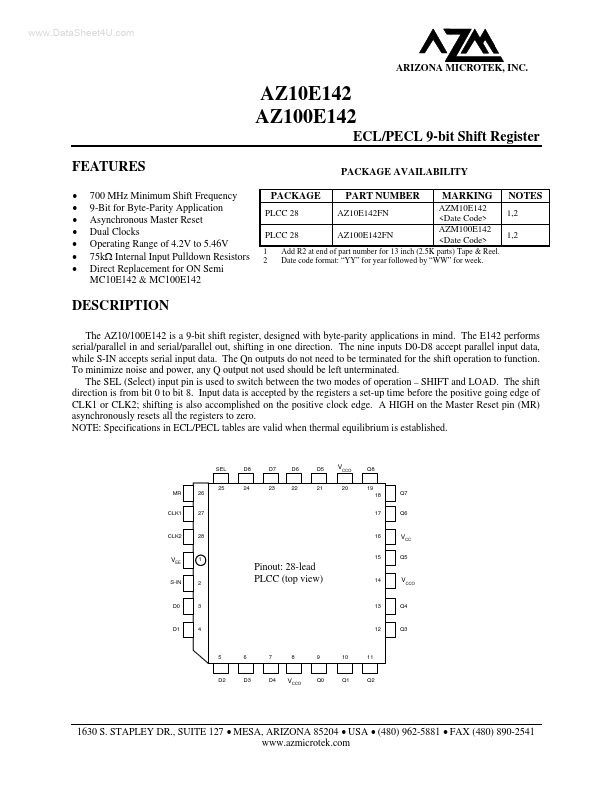

- 700 MHz Minimum Shift Frequency 9-Bit for Byte-Parity Application Asynchronous Master Reset Dual Clocks Operating Range of 4.2V to 5.46V 75kΩ Internal Input Pulldown Resistors Direct Replacement for ON Semi MC10E142 & MC100E142 PACKAGE

PLCC 28 PLCC 28

1 2

PACKAGE AVAILABILITY PART NUMBER

AZ10E142FN AZ100E142FN

MARKING

AZM10E142 <Date Code> AZM100E142 <Date Code>

NOTES

1,2 1,2

Add R2 at end of part number for 13 inch (2.5K parts) Tape & Reel. Date code format: “YY” for year followed by “WW” for week.

DESCRIPTION

The AZ10/100E142 is a 9-bit shift register, designed with byte-parity applications in mind. The E142 performs serial/parallel in and serial/parallel out, shifting in one direction. The nine inputs D0-D8 accept parallel input data, while S-IN accepts serial input data. The Qn outputs do not need to be terminated for the shift operation to function. To minimize noise and power, any Q output not used should be left unterminated. The SEL (Select) input pin is used to switch between the two modes of operation

- SHIFT and LOAD. The shift direction is from bit 0 to bit 8. Input data is accepted by the registers a set-up time before the positive going edge of CLK1 or CLK2; shifting is also acplished on the positive clock edge. A HIGH on the Master Reset pin (MR) asynchronously resets all the registers to zero. NOTE: Specifications in ECL/PECL tables are valid when thermal equilibrium is established.

SEL 25 26

D8 24

D7 23

D6 22

D5 21

VCCO

Q8 19 18...