AZ100E111

Overview

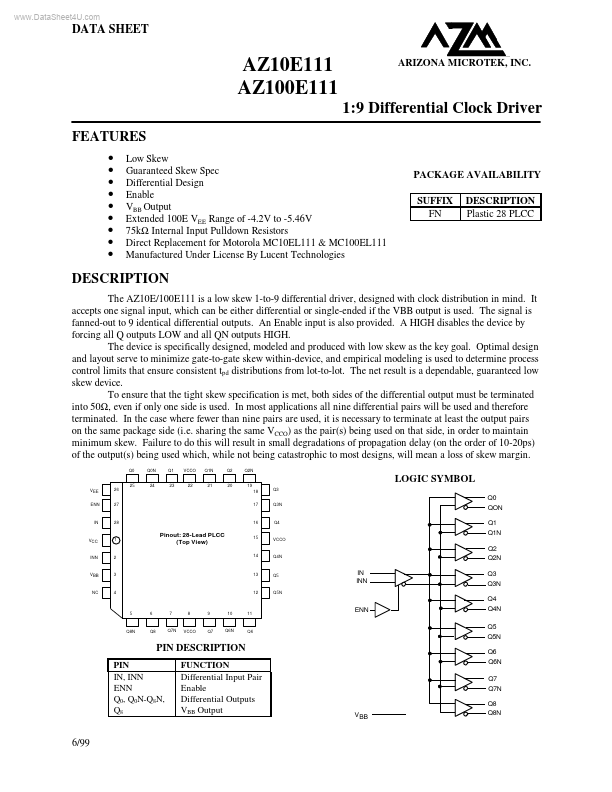

The AZ10E/100E111 is a low skew 1-to-9 differential driver, designed with clock distribution in mind. It accepts one signal input, which can be either differential or single-ended if the VBB output is used.

- Low Skew Guaranteed Skew Spec Differential Design Enable VBB Output Extended 100E VEE Range of -4.2V to -5.46V 75kΩ Internal Input Pulldown Resistors Direct Replacement for Motorola MC10EL111 & MC100EL111 Manufactured Under License By Lucent Technologies