MAX96752

Description

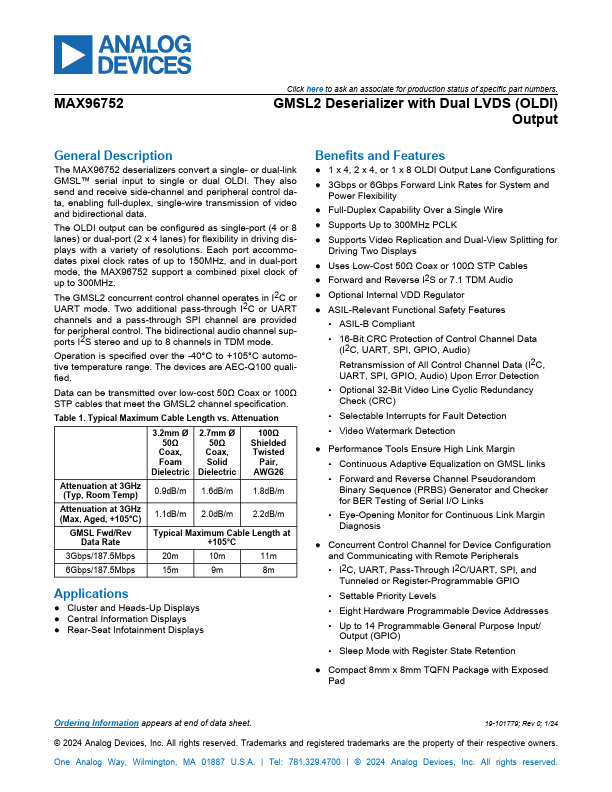

The MAX96752 deserializers convert a single- or dual-link GMSL™ serial input to single or dual OLDI. They also send and receive side-channel and peripheral control data, enabling full-duplex, single-wire transmission of video and bidirectional data.

Key Features

- 1 x 4, 2 x 4, or 1 x 8 OLDI Output Lane Configurations

- 3Gbps or 6Gbps Forward Link Rates for System and Power Flexibility

- Full-Duplex Capability Over a Single Wire

- Supports Up to 300MHz PCLK

- Supports