| Part | ADSP-TS101S |

|---|---|

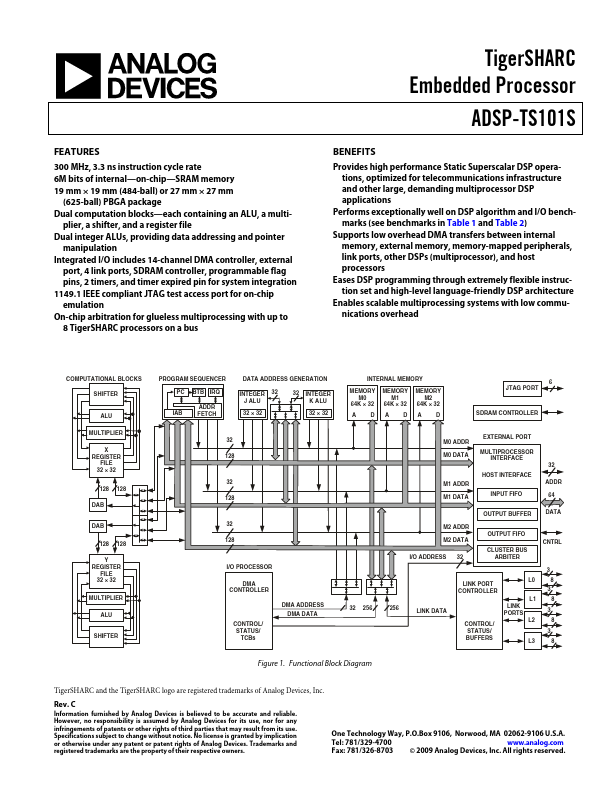

| Description | TigerSHARC Embedded Processor |

| Manufacturer | Analog Devices |

| Size | 472.17 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| RK3588 | Rockchip | high performance processor |

| BP1048B2 | MVSILICON | High-performance 32-bit Bluetooth audio application processor |

| RV1106 | Rockchip | highly integrated vision processor SoC |