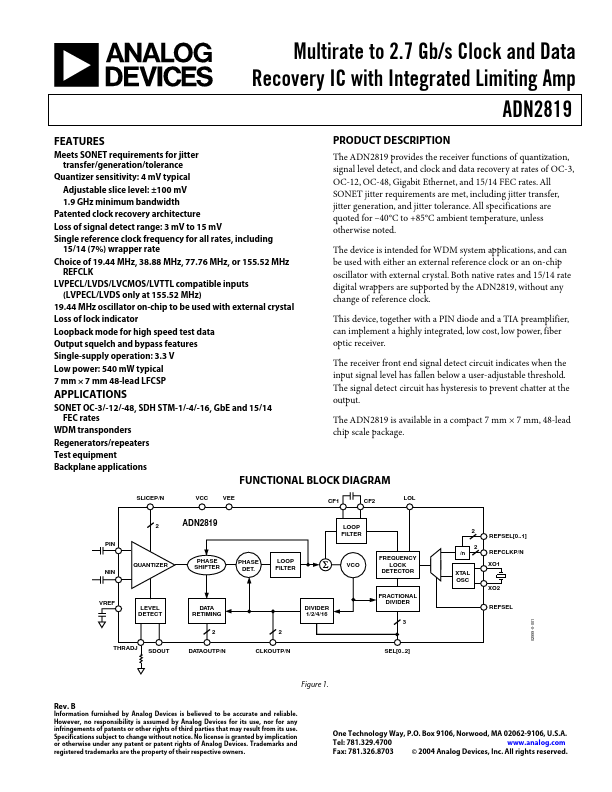

ADN2819 Description

The ADN2819 provides the receiver functions of quantization, signal level detect, and clock and data recovery at rates of OC-3, OC-12, OC-48, Gigabit Ethernet, and 15/14 FEC rates. All SONET jitter requirements are met, including jitter transfer, jitter generation, and jitter tolerance. All specifications are quoted for 40°C to +85°C ambient temperature, unless otherwise noted.