AD9528

AD9528 is JESD204B/JESD204C Clock Generator manufactured by Analog Devices.

Data Sheet AD9528

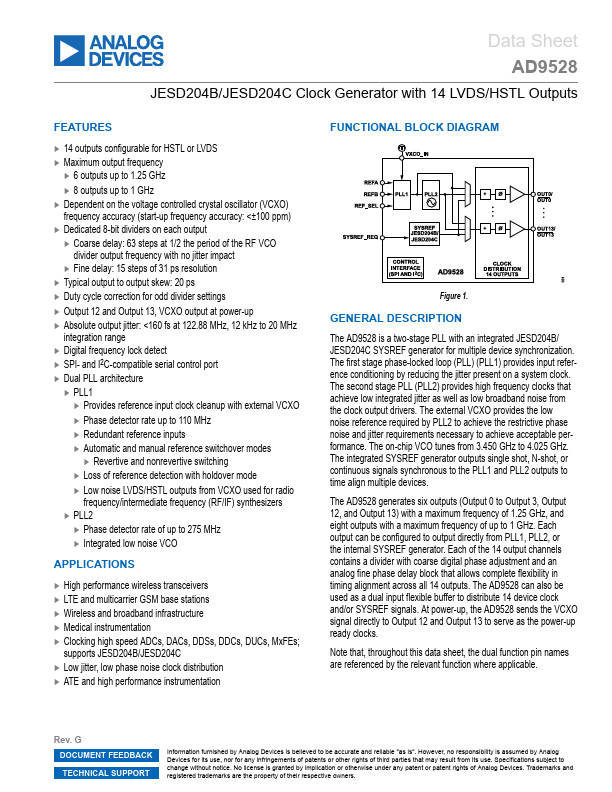

JESD204B/JESD204C Clock Generator with 14 LVDS/HSTL Outputs

Features

- 14 outputs configurable for HSTL or LVDS

- Maximum output frequency

- 6 outputs up to 1.25 GHz

- 8 outputs up to 1 GHz

- Dependent on the voltage controlled crystal oscillator (VCXO) frequency accuracy (start-up frequency accuracy: <±100 ppm)

- Dedicated 8-bit dividers on each output

- Coarse delay: 63 steps at 1/2 the period of the RF VCO divider output frequency with no jitter impact

- Fine delay: 15 steps of 31 ps resolution

- Typical output to output skew: 20 ps

- Duty cycle correction for odd divider settings

- Output 12 and Output 13, VCXO output at power-up

- Absolute output jitter: <160 fs at 122.88 MHz, 12 k Hz to 20 MHz integration range

- Digital frequency lock detect

- SPI- and I2C-patible serial control port

- Dual PLL architecture

- PLL1

- Provides reference input clock cleanup with external VCXO

- Phase detector rate up to 110 MHz

- Redundant reference inputs

- Automatic and manual reference switchover modes

- Revertive and nonrevertive switching

- Loss of reference detection with holdover mode

- Low noise LVDS/HSTL outputs from VCXO used for radio frequency/intermediate frequency (RF/IF) synthesizers

- PLL2

- Phase detector rate of up to 275 MHz

- Integrated low noise VCO

APPLICATIONS...