AD9267 Overview

Description

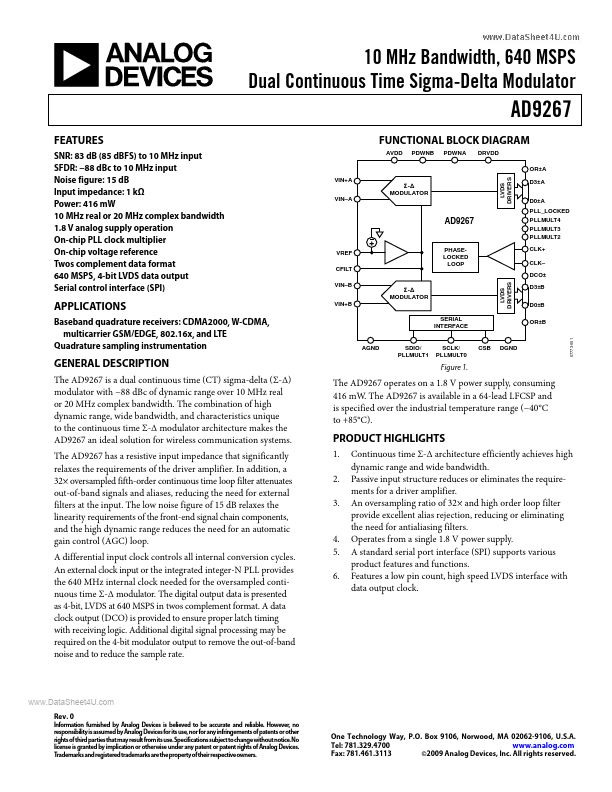

The AD9267 is a dual continuous time (CT) sigma-delta (Σ-Δ) modulator with -88 dBc of dynamic range over 10 MHz real or 20 MHz complex bandwidth. The combination of high dynamic range, wide bandwidth, and characteristics unique to the continuous time Σ-Δ modulator architecture makes the AD9267 an ideal solution for wireless communication systems.