AD6641 Overview

Description

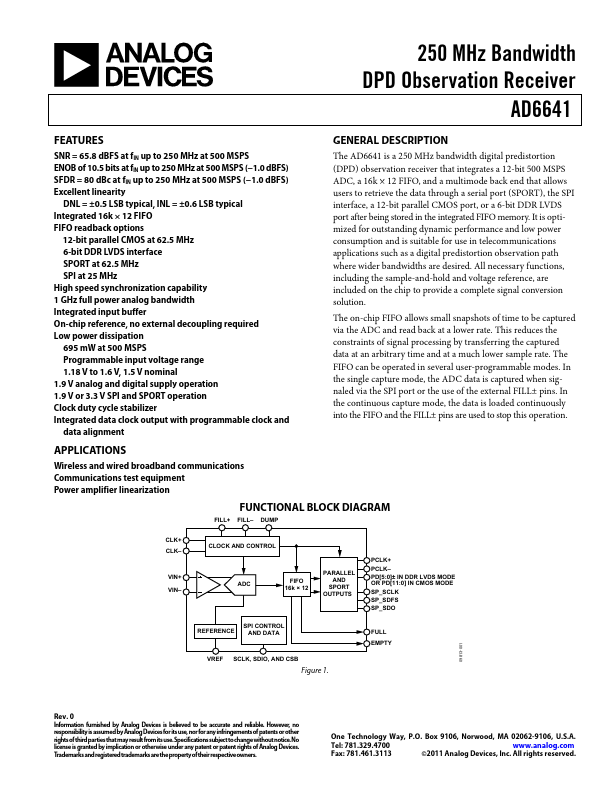

The AD6641 is a 250 MHz bandwidth digital predistortion (DPD) observation receiver that integrates a 12-bit 500 MSPS ADC, a 16k × 12 FIFO, and a multimode back end that allows users to retrieve the data through a serial port (SPORT), the SPI interface, a 12-bit parallel CMOS port, or a 6-bit DDR LVDS port after being stored in the integrated FIFO memory. It is optimized for outstanding dynamic performance and low power consumption and is suitable for use in telecommunications applications such as a digital predistortion observation path where wider bandwidths are desired.