Datasheet Summary

PE12316 Triple Incremental Encoder

February 6, 2003 Preliminary (Version 1.1)

Features

:

- -

- -

- -

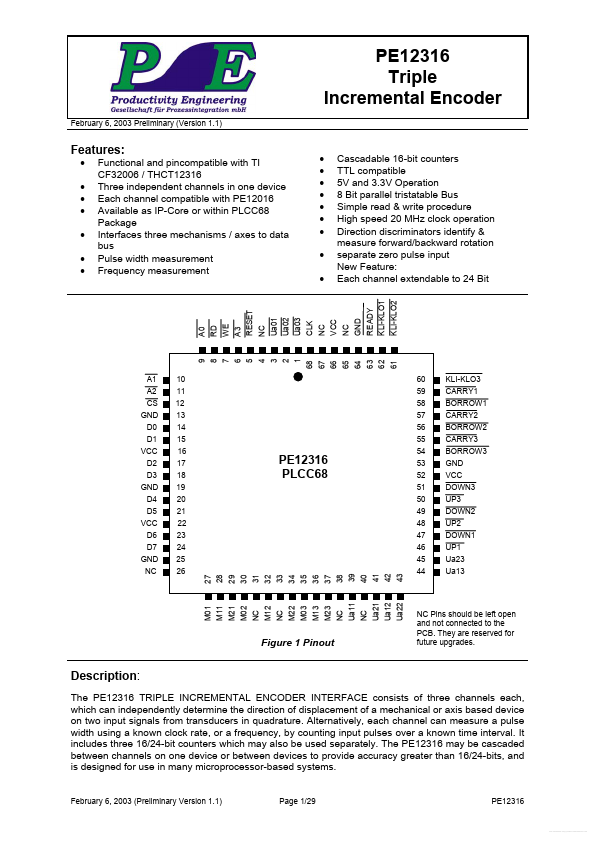

- Functional and pinpatible with TI CF32006 / THCT12316 Three independent channels in one device Each channel patible with PE12016 Available as IP-Core or within PLCC68 Package Interfaces three mechanisms / axes to data bus Pulse width measurement Frequency measurement

- -

- -

- -

- -

- Cascadable 16-bit counters TTL patible 5V and 3.3V Operation 8 Bit parallel tristatable Bus Simple read & write procedure High speed 20 MHz clock operation Direction discriminators identify & measure forward/backward rotation separate zero pulse input New Feature: Each channel extendable to 24...