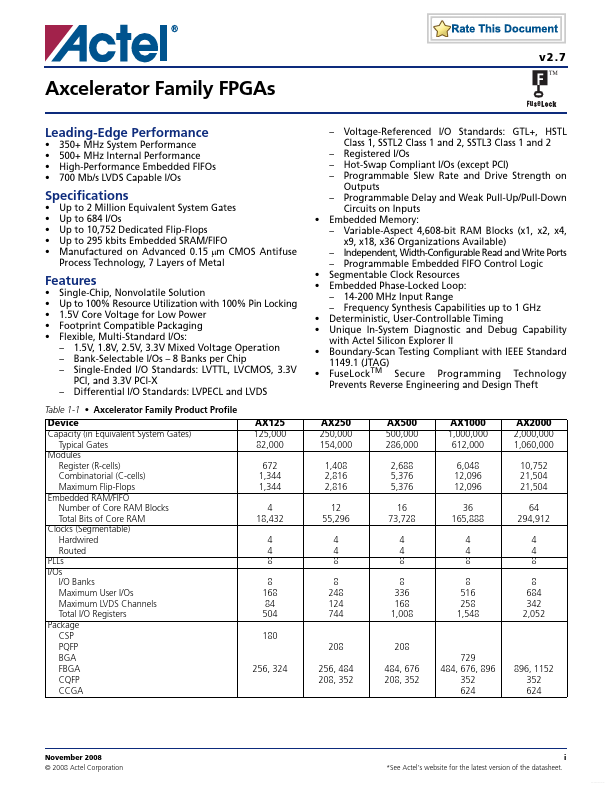

| Part | AX2000 |

|---|---|

| Description | Axcelerator Family FPGAs |

| Manufacturer | Actel |

| Size | 2.40 MB |

Pricing from 1330.26 USD, available from DigiKey and NAC Semi.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| DigiKey | 24 | 1+ : 1330.26 USD | View Offer |

| NAC Semi | 2 | 27+ : 1163.99 USD | View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| AX2002 | Philips Semiconductors | Portable CD Player |

| AX2011 | Philips Semiconductors | Portable CD Player |

| AX2003 | Philips Semiconductors | Portable CD Player |

| AX2001 | Philips Semiconductors | Portable CD Player |

| AX2000 | Philips Semiconductors | Portable CD Player |