ATR0600

Description

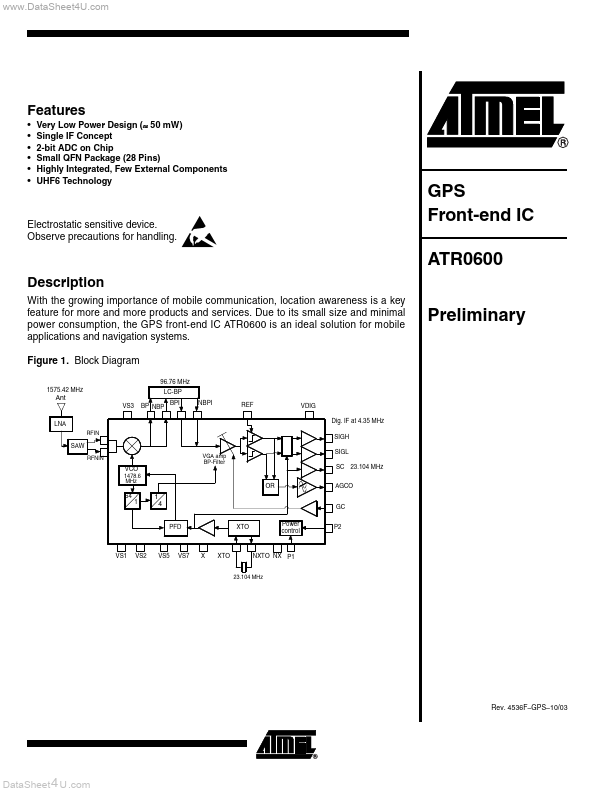

With the growing importance of mobile communication, location awareness is a key feature for more and more products and services. Due to its small size and minimal power consumption, the GPS front-end IC ATR0600 is an ideal solution for mobile applications and navigation systems.

Key Features

- Very Low Power Design (≈ 50 mW) Single IF Concept 2-bit ADC on Chip Small QFN Package (28 Pins) Highly Integrated, Few External Components UHF6 Technology Electrostatic sensitive device. Observe precautions for handling. GPS Front-end IC ATR0600