AT91SAM7S512 Overview

Key Specifications

Package: LQFP

Mount Type: Surface Mount

Pins: 64

Max Voltage (typical range): 3.6 V

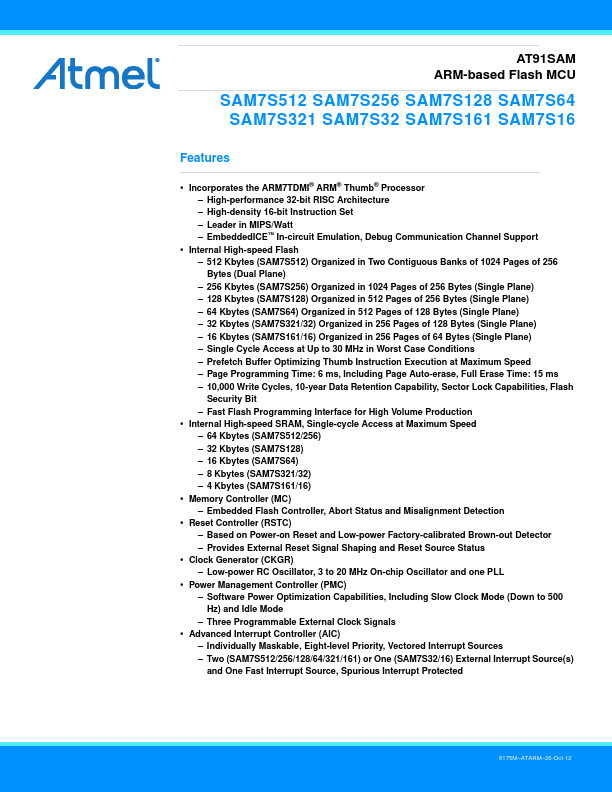

Key Features

- Memory Controller (MC) – Embedded Flash Controller, Abort Status and Misalignment Detection

- Clock Generator (CKGR) – Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL