MT5C1008 Overview

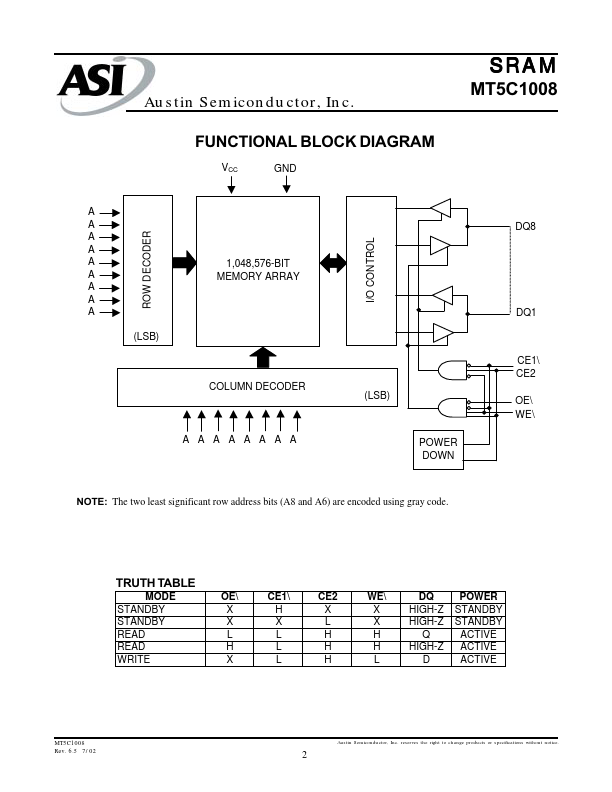

The MT5C1008 SRAM employs high-speed, low power CMOS designs using a four-transistor memory cell, and are fabricated using double-layer metal, double-layer polysilicon technology. For design flexibility in high-speed memory applications, this device offers dual chip enables (CE1, CE2) and output enable (OE). These control pins can place the outputs in High-Z for additional flexibility in system design.

MT5C1008 Key Features

- All inputs and outputs are TTL patible

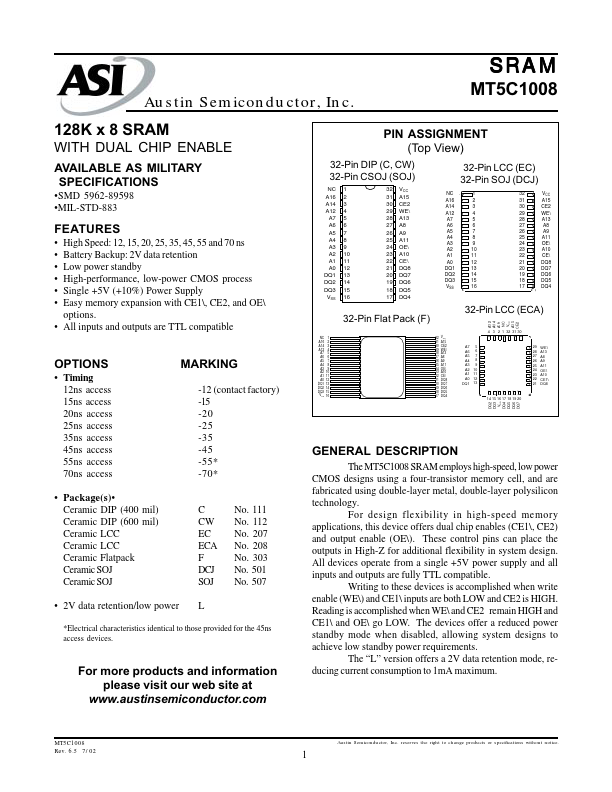

- Package(s)- Ceramic DIP (400 mil) Ceramic DIP (600 mil) Ceramic LCC Ceramic LCC Ceramic Flatpack Ceramic SOJ Ceramic SOJ

- 2V data retention/low power

- 12 (contact factory) -15 -20 -25 -35 -45 -55- -70

MT5C1008 Applications

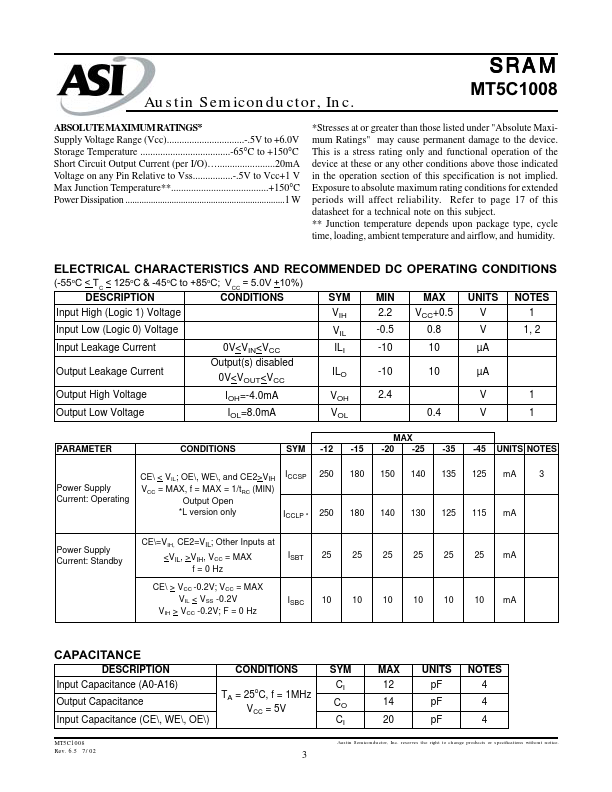

- Electrical characteristics identical to those provided for the 45ns access devices