| Part | ODTSXX12 |

|---|---|

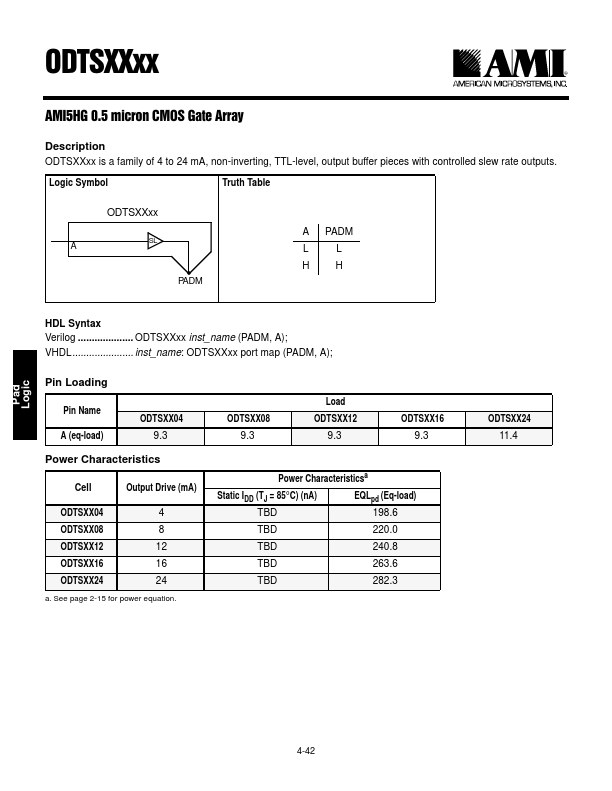

| Description | CMOS Gate Array |

| Manufacturer | AMI |

| Size | 23.70 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CTA2P1N | Diodes Incorporated | COMPLEX TRANSISTOR ARRAY |

| CTA2N1P | Diodes Incorporated | COMPLEX TRANSISTOR ARRAY |

| 7003 | Allegro MicroSystems | HIGH-VOLTAGE/ HIGH-CURRENT DARLINGTON ARRAY |