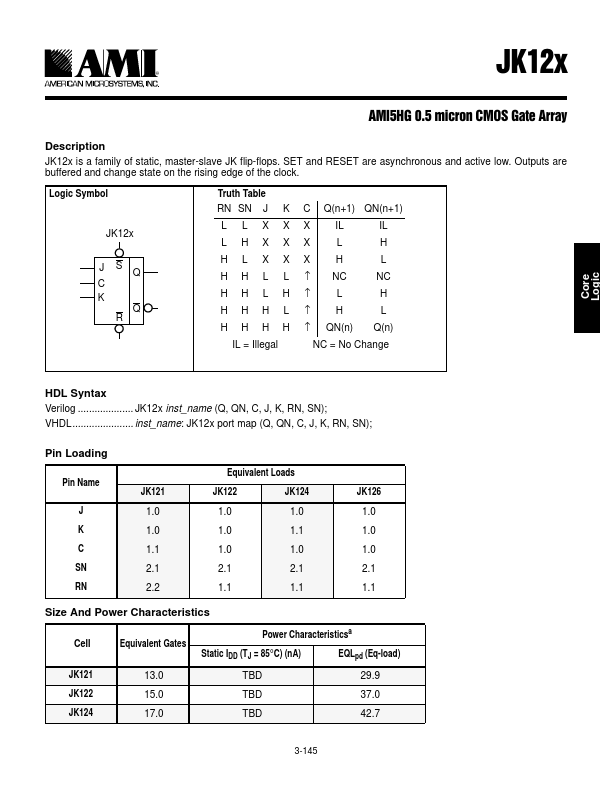

| Part | JK124 |

|---|---|

| Description | CMOS Gate Array |

| Manufacturer | AMI |

| Size | 48.38 KB |

Available from Venkel.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Venkel | -4 | - | View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| CTA2P1N | Diodes Incorporated | COMPLEX TRANSISTOR ARRAY |

| CTA2N1P | Diodes Incorporated | COMPLEX TRANSISTOR ARRAY |

| 7003 | Allegro MicroSystems | HIGH-VOLTAGE/ HIGH-CURRENT DARLINGTON ARRAY |