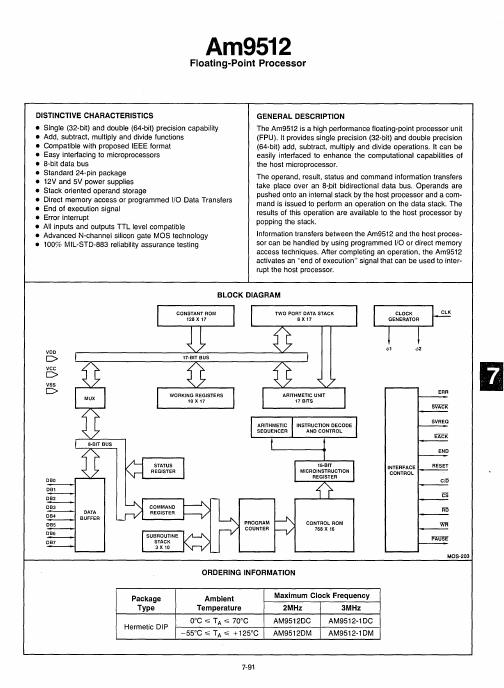

Am9512 Overview

The Am9512 is a high performance floating-point processor unit (FPU). It provides single precision (32-bit) and double precision (64-bit) add, subtract, multiply and divide operations. It can be easily interfaced to enhance the putational capabilities of the host microprocessor.

Am9512 Key Features

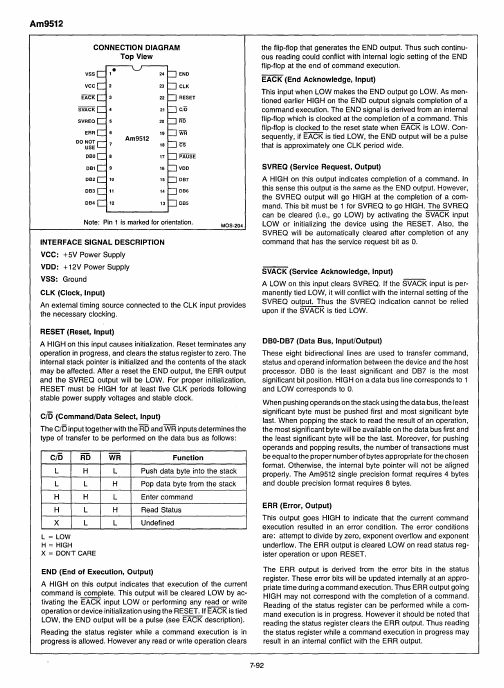

- l L = LOW H = HIGH X = DON'T CARE Function Push data byte into the stack Pop data byte from the stack Ente