AK491024G

AK491024G is 1048576 Word x 9 Bit CMOS Dynamic Random Access Memory manufactured by ACCUTEK.

- Part of the AK491024S comparator family.

- Part of the AK491024S comparator family.

MICROCIRCUIT CORPORATION

DESCRIPTION

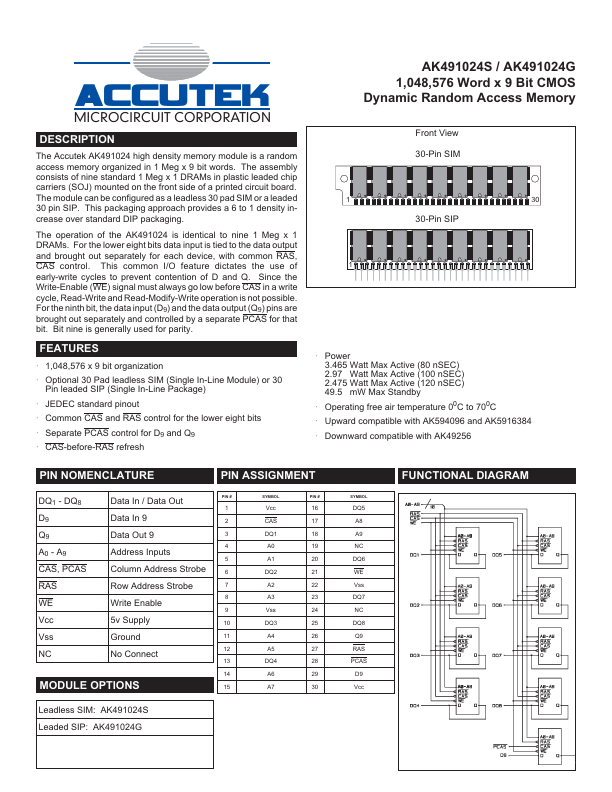

The Accutek AK491024 high density memory module is a random access memory organized in 1 Meg x 9 bit words. The assembly consists of nine standard 1 Meg x 1 DRAMs in plastic leaded chip carriers (SOJ) mounted on the front side of a printed circuit board. The module can be configured as a leadless 30 pad SIM or a leaded 30 pin SIP. This packaging approach provides a 6 to 1 density increase over standard DIP packaging. The operation of the AK491024 is identical to nine 1 Meg x 1 DRAMs. For the lower eight bits data input is tied to the data output and brought out separately for each device, with mon RAS, CAS control. This mon I/O feature dictates the use of early-write cycles to prevent contention of D and Q. Since the Write-Enable (WE) signal must always go low before CAS in a write cycle, Read-Write and Read-Modify-Write operation is not possible. For the ninth bit, the data input (D9) and the data output (Q9) pins are brought out separately and controlled by a separate PCAS for that bit. Bit nine is generally used for parity.

ACCUTEK

AK491024S / AK491024G 1,048,576 Word x 9 Bit CMOS Dynamic Random Access Memory

Front View 30-Pin SIM

30-Pin SIP

Features

- 1,048,576 x 9 bit organization

- Optional 30 Pad leadless SIM (Single In-Line Module) or 30 Pin leaded SIP (Single In-Line Package)

- JEDEC standard pinout

- mon CAS and RAS control for the lower eight bits

- Separate PCAS control for D9 and Q9

- CAS-before-RAS refresh

- Power 3.465 Watt Max Active (80 n SEC) 2.97 Watt Max Active (100 n SEC) 2.475 Watt Max Active (120 n SEC) 49.5 m W Max Standby

- Operating free air temperature 00C to 700C

- Upward patible with AK594096 and AK5916384

- Downward patible with AK49256

PIN NOMENCLATURE

DQ1

- DQ8 D9 Q9 A0

- A9 CAS, PCAS RAS WE Vcc Vss NC Data In / Data Out Data In 9 Data Out 9 Address Inputs Column Address Strobe Row Address Strobe Write Enable 5v Supply Ground No Connect

PIN ASSIGNMENT

PIN # SYMBOL PIN...