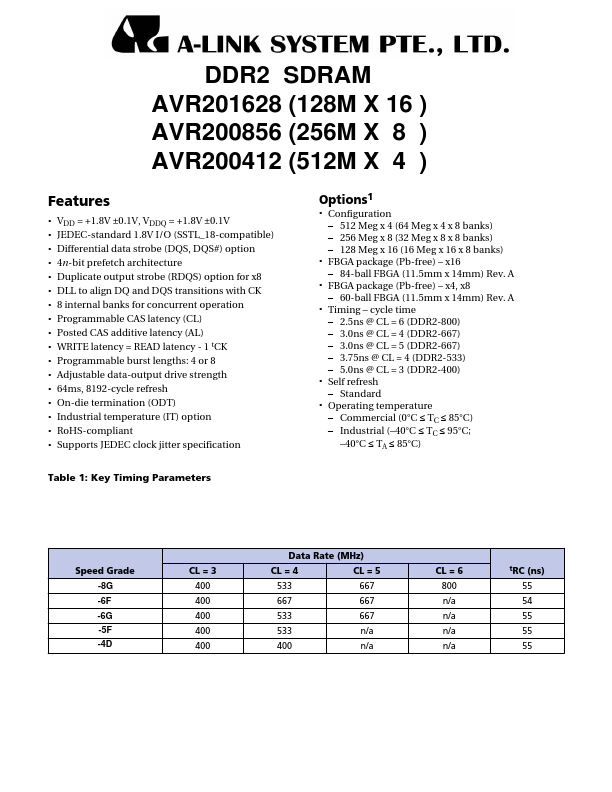

AVR200856

Key Features

- VDD = +1.8V ±0.1V, VDDQ = +1.8V ±0.1V

- JEDEC-standard 1.8V I/O (SSTL_18-compatible)

- Differential data strobe (DQS, DQS#) option

- 4n-bit prefetch architecture

- Duplicate output strobe (RDQS) option for x8

- DLL to align DQ and DQS transitions with CK

- 8 internal banks for concurrent operation

- Programmable CAS latency (CL)

- Posted CAS additive latency (AL)

- WRITE latency = READ latency