H9TP32A4GDBCPR Overview

and is subject to change without notice. SK hynix does not assume any responsibility for use of circuits described. No patent licenses are implied.

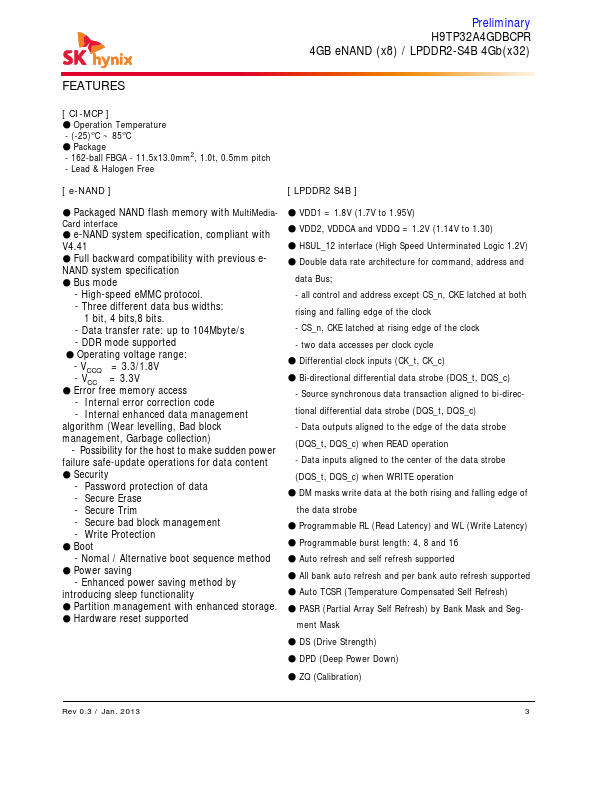

H9TP32A4GDBCPR Key Features

- Operation Temperature

- (-25)oC ~ 85oC

- Package

- 162-ball FBGA

- 11.5x13.0mm2, 1.0t, 0.5mm pitch

- Lead & Halogen Free

- Packaged NAND flash memory with MultiMediaCard interface

- e-NAND system specification, pliant with V4.41

- Full backward patibility with previous eNAND system specification

- Bus mode